Development of new voltage-controlled writing method for nonvolatile solid-state magnetic memory

As part of the Impulsing PAradigm Change through disruptive Technologies Program (ImPACT) (Program Manager: Masashi Sahashi) led by the Council for Science, Technology and Innovation of the Cabinet Office, an R&D team consisting of Shinobu Fujita, the Chief Research Officer of Toshiba Corporation's Corporate Research & Development Center (Center Director: Osamu Hori) and Takayuki Nozaki, Leader of the voltage-driven spintronics Team, spintronics Research Center (Director: Shinji Yuasa), National Institute of Advanced Industrial Science and Technology (AIST; Director: Ryoji Chubachi), have developed a new write method that reduces the write error rate of "voltage torque MRAM," which is a type of voltage-controlled nonvolatile magnetic memory.

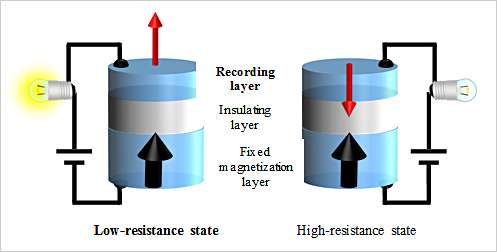

The voltage-driven spintronics team in AIST previously developed a magnetic tunnel junction (MTJ) element, in which magnetization reversal can be controlled by fast voltage pluses, and has been developing a new type of voltage-controlled magnetic memory, "voltage torque MRAM." voltage torque MRAM is expected to offer dramatically lower power consumption than conventional current-controlled magnetic memory (STT-MRAM), but reducing the write error rate has been a major challenge in terms of practical application of the technology.

In this work, the AIST team and an R&D team in Toshiba developed a method that suppresses the occurrence of write failures due to thermal fluctuations and reduces the write error rate by applying pulse voltage with the reversed polarity of the write voltage before and after the pulse voltage applied during writes. A new write circuit has also been developed to implement this method. This result is expected to lead to larger capacity last-level caches and increased processor performance.

The technical details of this result will be presented at the International Electron Devices Meeting (IEDM) on 7 December 2016 in San Francisco, California. The results will be published in the "IEDM 2016 Technical Digest" scheduled for release 3 December 2016 (Pacific Standard Time).

Reducing the power consumption of IT devices is of prime importance in terms of conserving the global environment while providing the richness of social activity. In the field of electronics, a key technology that is attracting a great deal of attention for achieving these goals is nonvolatile memory that does not require power to store data. In the field of spintronics, development has been progressing on MRAM nonvolatile magnetic memory that utilizes the nonvolatile nature of magnets and is recognized as the only nonvolatile memory offering high capacity, high speed, and highly repeatable operation.

However, presently available magnetic memories are "current-controlled," which means that data are written (i.e. magnetization is reversed) by supplying current to the MTJ element. This creates the problem that power consumption for writing is larger in the magnetic memory than in semiconductor memory. To fundamentally resolve this problem, the voltage-driven spintronics team has been working on developing "voltage torque MRAM," which is voltage-controlled and uses an extremely small amount of power during writing. This type of MRAM, which requires zero stand-by power and very little active power, is being developed through the ImPACT project "Achieving Ultimate Green IT Devices with Long Usage Time without Charging (Program Manager: Masashi Sahashi)."

The voltage-driven spintronics team previously worked on developing technology for control of magnetic anisotropy by applying voltage to ultra-thin metallic magnetic films, as well as new magnetization reversal control methods that use this technology (refer to the JST press release of 10 December 2015, "Proof of Stable Operation of voltage Write Method Nonvolatile Memory and Evaluation of the Write Error Rate"). One thing that is particularly important for making voltage torque MRAM practical is minimizing the failure rate when writing data (i.e., minimizing the write error rate). The above-mentioned press release details material design guidelines for achieving an error rate of 10-10 to 10-15 as a rough guide for practical application, and ImPACT is currently making progress in developing materials that following these guidelines.

In the present work, the voltage-driven spintronics team in AIST and the R&D team in Toshiba developed methods for reducing the write error rate and performed circuit design that achieves a low write error rate by improving material characteristics through the mechanism of applying a pulse voltage having a devised waveform during writing.

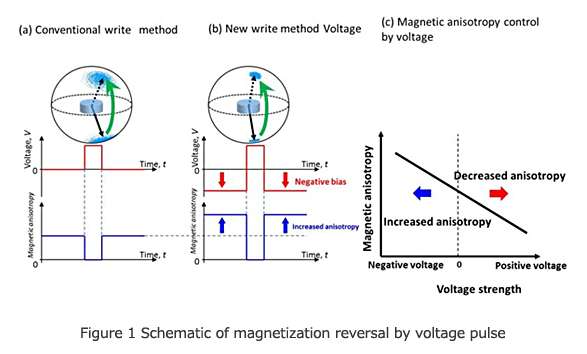

Figure 1 shows schematic diagrams of (a) the conventional method and (b) the new method for voltage-controlled writing. In Fig. 1(a), the magnetization stabilizes in the downward facing (or upward facing) direction, where the magnetic anisotropy energy is the lowest when a voltage is not applied. In this way, 1 bit of data is stored in a nonvolatile manner. Then, when a positive voltage pulse is applied, the magnetization starts rotational motion due to the magnetic anisotropy instantly becoming zero. If the pulse voltage is shut down exactly when the magnetization is facing the opposite direction from the initial state, the magnetization can be reversed to the upward facing (or downward facing) stable point at the opposite side, and thus the data is written. This gives the basic operation of magnetization reversal (i.e. writing data) by voltage. Note that the magnetization direction fluctuates both in the initial state before the magnetization reversal and in the final state after the reversal because of thermal energy. As the thermal fluctuations become larger, write error rate can increase. In other words, the write error rate can be reduced by suppressing thermal fluctuations of the magnetization in the initial and final states.

The basic method for minimizing the thermal fluctuations is to use a metal magnetic material with a large magnetic anisotropy to increase the stability to the magnetization against thermal energy, but there are limits to merely improving the metal magnetic material.

The method newly developed in this work reduces the write error rate by using voltage to increase the perpendicular magnetic anisotropy. Figure 1(c) shows a schematic of changing the magnetic anisotropy by using voltage. Because the magnetic anisotropy changes linearly as a function of applied voltage, it becomes smaller for positive voltages and larger for negative voltages. In conventional voltage writing, magnetization reversal is performed by using only the reduction in magnetic anisotropy by application of a positive voltage pulse. In the new method, on the other hand, the write error rate is greatly reduced by suppressing thermal fluctuations of magnetization in the initial and final states by applying a negative voltage in these states, thereby increasing the magnetic anisotropy as shown in Fig. 1(b).

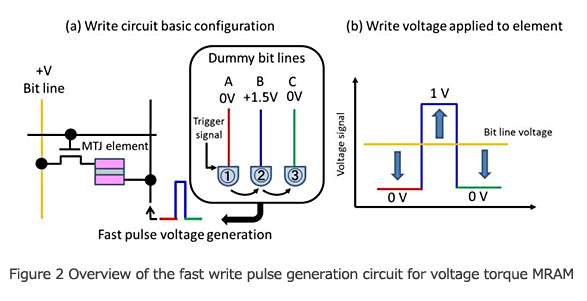

Note that to implement the above method, it is necessary to accurately apply a pulse voltage that has a pulse width of around 1 nanosecond and steep reverse polarity of around several hundred picoseconds to each of the elements within the memory array. In circuits for writing conventional magnetic memory, it has been difficult to generate high-speed voltage pulse with an accurately controlled waveform, because the waveform of the voltage pulses can be degraded because of the influence of resistance and capacitance components of memory elements and wiring, which make the quick switching of the voltage polarity difficult. The team therefore developed a special write circuit for voltage torque MRAM that can generate fast pulse voltages with reverse polarity. Figure 2(a) shows an overview of the fast voltage pulse generation. The three stages of the pulse voltages that will be switched between at high speed are set up in advance on three wires (called dummy bit lines A, B, and C). Each of these wires has a loop structure with respect to the write instruction (trigger signal), where the next signal is triggered by previous signal. In other words, this is a mechanism that applies each of the wires to the element sequentially in the order A → B → C. This enables the write pulse voltage to be accurately controlled at high speed without delays or loss of the waveform shape. Figure 2(a) shows an example for A= 0 V, B = 1.5 V, and C = 0 V, which can generate a 1.5 V pulse voltage with extremely steep rising (and falling) edges and short pulse width (A and C can also be set to values other than 0 V). At this point, if a voltage of 1 V, for example, is applied to the reverse side bit lines, then the actual voltage signal applied to the element will be -1 V → 0.5 V → -1 V, and it would be possible to accurately apply a high-speed pulse with reverse polarity (Fig. 2(b)).

Furthermore, memory circuit operation time can be reduced by simultaneously performed reading while applying the reverse polarity pulse voltage. This makes it possible to read the recorded data of the initial state and instantly skip the write process if there is no need to write the data, and also to quickly perform the error correction process called "verify," in which the recorded data is checked again after writing and is written again in the event of a write error. Combination of these error rate reduction methods can achieve the target error rate of 10-10 to 10-15 for practical applications.

In addition to reducing the write error rate, the team also developed a new read circuit that utilizes the phenomenon where the resistance of the MTJ element changes for read voltages.

Great improvement in write and read error rates was demonstrated by leading-edge CMOS circuit simulations based on measurement data for a fabricated memory element of diameter 30 nm. It was shown that if the efficiency of the voltage-controlled magnetic anisotropy can be enhanced by three times than the present value, it will be possible to apply this technology in ultra-large last-level caches with memory capacities of 1 to 2 Gbit.

The voltage-spintronics team in AIST and the R&D team in Toshiba is aiming to demonstrate voltage-controlled magnetic anisotropy that satisfies the requirements for large-capacity last-level cache or even larger capacity main memory in actual MTJ elements of several tens of nanometers, based on the new directions opened by this research. And further development for higher performance circuit systems will also be continued.

More information:

"Novel Voltage Controlled MRAM (VCM) with Fast Read/Write Circuits for Ultra Large Last Level Cache" IEDM 2016 Technical Digest, IEDM 2016 (International Electron Devices Meeting), 7 December 2016 (Wednesday)

Provided by Toshiba